# Toward Low-Power Electronics: Tunneling Phenomena in Transition Metal Dichalcogenides

Saptarshi Das,<sup>†,‡,\*,§</sup> Abhijith Prakash,<sup>‡,§</sup> Ramon Salazar,<sup>‡</sup> and Joerg Appenzeller<sup>‡</sup>

<sup>†</sup>Center for Nanoscale Material, Argonne National Laboratory, Lemont, Illinois 60439, United States and <sup>‡</sup>Birck Nanotechnology Center, Purdue University, West Lafayette, Indiana 47907, United States. <sup>§</sup>These authors have contributed equally to this work.

**ABSTRACT** In this article, we explore, experimentally, the impact of band-to-band tunneling on the electronic transport of double-gated WSe<sub>2</sub> field-effect transistors (FETs) and Schottky barrier tunneling of holes in back-gated MoS<sub>2</sub> FETs. We show that by scaling the flake thickness and the thickness of the gate oxide, the tunneling current can be increased by several orders of magnitude. We also perform numerical calculations based on Landauer formalism and WKB approximation to explain our experimental findings. Based on our simple model, we discuss the impact of band gap and effective mass on the band-to-band tunneling current and evaluate the performance limits for a set of dichalcogenides in the context of tunneling transistors for low-power applications. Our findings suggest that WTe<sub>2</sub> is an excellent choice for tunneling field-effect transistors.

KEYWORDS: tunneling · transition metal dichalcogenides · transistor · low power

or decades, the semiconductor industry has been driven by the central objective of scaling down the channel dimensions of transistors in order to enhance their speed and packing densities while preserving an inverse subthreshold swing (defined as the gate voltage required to change the drain current by an order of magnitude) close to 60 mV/decade to minimize the power dissipation.<sup>1–3</sup> While silicon has successfully been used in this context in the past, novel low-dimensional materials that encompass semiconducting nanowires,<sup>4,5</sup> nanotubes,<sup>6,7</sup> III–V compound semiconductors,<sup>8</sup> graphene,<sup>9,10</sup> and more recently the large family of transition metal dichalcogenides such as MoS<sub>2</sub>, WSe<sub>2</sub>, and others<sup>11–14</sup> are now frequently discussed as options for continued scaling beyond the 10 nm technology node. Moreover, recent developments indicate that innovative device ideas that include tunneling field-effect transistors (TFETs),<sup>15–18</sup> impact ionization MOS devices, 19,20 suspended gate FETs, 21 and ferroelectric FETs<sup>22</sup> offer an opportunity to operate below the 60 mV/decade limit. Combining low-dimensional materials with these new concepts is thus a promising route toward new generations of electronic devices.

In this article, we evaluate the potential of transition metal dichalcogenides in the context of TFETs. In particular, first, we demonstrate Schottky barrier tunneling of holes in MoS<sub>2</sub> and band-to-band tunneling in WSe<sub>2</sub> and then use these experimental findings along with analytical calculations to make projections for TFETs based on various dichalcogenides.

## **RESULTS AND DISCUSSION**

Schottky Barrier Tunneling of Holes in MoS<sub>2</sub>. MoS<sub>2</sub> along with other transition metal dichalcogenides has generated a lot of interest in the device community due to their excellent electrostatic integrity that allows for aggressive channel length scaling. These novel two-dimensional layered semiconductors are naturally occurring ultrathin body materials similar to graphene, but with the added advantage of having a significant band gap which is essential for logic applications.<sup>23–26</sup> Numerous articles have been published arguing about the potential of MoS<sub>2</sub> for future nanoelectronics applications.<sup>27–31</sup> In our earlier reports, we have

\* Address corresondence to das@anl.gov, das.sapt@gmail.com.

Received for review November 21, 2013 and accepted January 6, 2014.

Published online January 06, 2014 10.1021/nn406603h

© 2014 American Chemical Society

VOL.8 • NO.2 • 1681-1689 • 2014

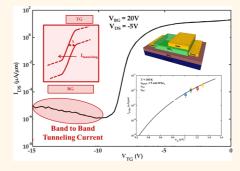

Figure 1. (a) False color optical image and (b) 3-D cartoon of a prototype back-gated  $MoS_2$  FET. (c) Transfer characteristics of representative  $\sim$ 3 nm thick  $MoS_2$  FET with Pd as source/drain contact electrodes and 20 nm SiO<sub>2</sub> as back gate. (d) Transfer characteristics of several  $\sim$ 3 nm thick  $MoS_2$  FETs illustrating device-to-device variations. (e–h) Energy band diagrams corresponding to different gate bias conditions marked in different color boxes in panel c.

evaluated several key aspects related to transistor design and carrier transport through MoS<sub>2</sub>-based FETs such as contact formation,<sup>31</sup> optimum layer thickness evaluation,<sup>32</sup> channel length scaling, and current distribution among the individual layers of multilayer MoS<sub>2</sub>.<sup>33,34</sup> However, in all these articles, we have focused on the electron transport through the MoS<sub>2</sub> FETs due to the absence of an appreciable hole branch in the device characteristics at negative gate voltages. Strong Fermi level pinning close to the conduction band of MoS<sub>2</sub> had been responsible for this experimental finding as it results in a large Schottky barrier height for hole injection into the valence band of MoS<sub>2</sub>. In this article, we show that by proper choice of flake thickness, oxide thickness, and biasing conditions, hole currents can be injected into the valence band of MoS<sub>2</sub> through tunneling. This tunneling, as mentioned before, occurs through a large Schottky barrier height which is similar to the band gap of this material and hence allows us to evaluate the potential of MoS<sub>2</sub> in the context of TFETs.

Figure 1a shows a false color optical image, and Figure 1b shows the 3-D device structure schematically of a prototype back-gated  $MoS_2$  FET used for our tunneling study. The 20 and 100 nm silicon dioxide (SiO<sub>2</sub>) substrates with underlying highly doped silicon were used as the back gate and palladium (Pd) with a subnanometer adhesive layer of titanium (Ti) was used as the source/drain metal contact. The channel length for all the devices was designed to be 4  $\mu$ m.

Figure 1c shows room temperature transfer characteristics of a representative device, and Figure 1d indicates how much device-to-device variations impact the current of  $\sim$ 3 nm thick MoS<sub>2</sub> FETs with 20 nm thick SiO<sub>2</sub> as the back gate oxide. Figure 1e-h illustrates the energy band diagrams corresponding to different gate biases (shown in semitransparent square boxes in Figure 1c) qualitatively. A large positive voltage was applied to the drain terminal ( $V_{DS} = 2.0 \text{ V}$ ) to facilitate hole injection from the drain terminal (Figure 1g,h). For large positive gate biases ( $V_{GS} > V_{FB}$ , where  $V_{\rm FB}$  is the flat band voltage), electrons are injected into the channel from the source terminal (Figure 1e). This electron current has two components-thermionic emission current over the top of the Schottky barrier (I<sub>N-thermionic</sub>) and the tunneling current through the Schottky barrier (I<sub>N-tunneling</sub>). As  $V_{\rm GS}$  is reduced to  $V_{\rm FB}$ , the electron tunneling current vanishes, as shown in Figure 1f. For  $V_{GS} < V_{FB}$ , the thermionic emission current starts to drop exponentially and the device enters into its OFF state. As  $V_{GS}$ is further reduced, holes can tunnel into the channel through the Schottky barrier at the drain terminal (Figure 1g). Note that the height of the Schottky barrier for hole injection into the valence band is  $\Phi_{\rm P} = E_{\rm G} - \Phi_{\rm N}$ , where  $E_{G}$  is the band gap of MoS<sub>2</sub> and  $\Phi_{N}$  is the Schottky barrier height for electron injection into the conduction band which had been determined previously by us as  $\sim$ 250 meV for Pd on MoS<sub>2</sub>.<sup>31</sup>

Figure 2a shows the room temperature transfer characteristics of 3, 6, and 10 nm thick  $MoS_2$  FETs back-gated through a 100 nm  $SiO_2$  film. For the 10 nm thick  $MoS_2$  flake, the hole tunneling current is below the noise floor for the entire range of  $V_{GS}$  and

VOL.8 • NO.2 • 1681-1689 • 2014

JAI

www.acsnano.org

| t <sub>OX</sub> (nm) | t <sub>BODY</sub> (nm) | V <sub>FB</sub> (V) | $V_{GS}$ - $V_{MIN}(V)$ | γ    | $V_{\text{DS}}(V)$ | $\Psi_{\text{DRIVE}} = q V_{\text{DS}} + q \left  \left( V_{\text{GS}} - V_{\text{MIN}} - V_{\text{FB}} \right) / \gamma \right  \text{ (eV)}$ | λ(nm) |

|----------------------|------------------------|---------------------|-------------------------|------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 100                  | 6                      | 5.0                 | -9.0                    | 21.0 | 4.0                | <b>4.7</b> (~ 5.0)                                                                                                                             | 24.5  |

|                      | 3                      | 8.0                 | -9.0                    | 18.5 | 4.0                | <b>4.9</b> (~ 5.0)                                                                                                                             | 17.3  |

| 20                   | 10                     | 2.8                 | -2.7                    | 7.6  | 2.0                | 2.7 (~ 3.0)                                                                                                                                    | 14.1  |

|                      | 6                      | 2.6                 | -2.7                    | 7.5  | 2.0                | 2.7 (~ 3.0)                                                                                                                                    | 10.9  |

|                      | 3                      | 1.8                 | -2.7                    | 7.2  | 2.0                | 2.6 (~ 3.0)                                                                                                                                    | 7.7   |

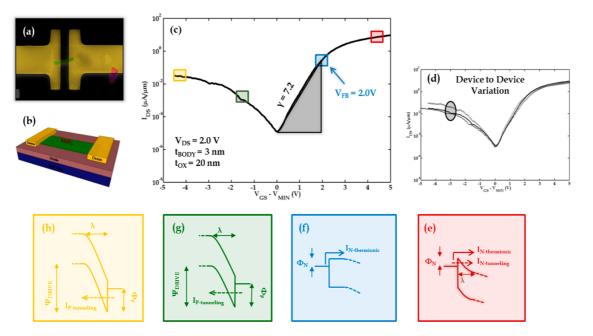

Figure 2. Room temperature transfer characteristics of a 3, 6, and 10 nm thick MoS<sub>2</sub> FET with Pd as source/drain contact electrodes on (a) 100 nm and (b) 20 nm SiO<sub>2</sub> as the back gate dielectric. (c) Simplified energy band diagram used to calculate the tunneling current within WKB approximation. (d) Experimental (squares and triangles) and simulated (solid lines) tunneling currents as a function of the screening length ( $\lambda$ ) for different drive voltages ( $\Psi_{\text{DRIVE}}$ ). (e) Table showing the extracted  $\Psi_{\text{DRIVE}}$  values from panels a and b.

was not used in our quantitative analysis. For the 6 and 3 nm thick MoS<sub>2</sub> flakes, the hole tunneling current, as expected, increased monotonically with the applied  $V_{

m GS}$ . The hole tunneling current was found to be  $\sim$ 1 imes $10^{-6}$  and  $\sim 3 \times 10^{-3} \,\mu$ A/ $\mu$ m for the 6 and 3 nm flakes, respectively, for  $V_{GS} - V_{MIN} = -9.0$  V. Figure 2b shows room temperature transfer characteristics of MoS<sub>2</sub> FETs for similar flake thicknesses but back-gated through a 20 nm SiO<sub>2</sub> layer. The hole tunneling currents in this case were found to be  ${\sim}9 \times 10^{-6}, {\sim}1 \times 10^{-4},$  and  $\sim$ 1  $\times$  10<sup>-2</sup>  $\mu$ A/ $\mu$ m for 10, 6, and 3 nm flakes, respectively, for  $V_{GS} - V_{MIN} = -2.7$  V. Our experimental data suggest that the tunneling current can be enhanced by scaling the oxide thickness and the flake thickness. In order to understand the magnitude of the hole tunneling currents, we have performed numerical calculations based on a simple analytical model described in the following equations.<sup>16,35,36</sup>

$$I_{\text{P1}} = q \int_{\Phi_{\text{p}}}^{\infty} M(E + \Psi_{\text{DRIVE}} - \Phi_{\text{p}}) f(E) dE \qquad (1a)$$

$$I_{P2} = q \int_{\Phi_{p} - E_{G}}^{\Phi_{p}} M(E + \Psi_{DRIVE} - \Phi_{p}) T_{WKB - 2}(E) f(E) dE$$

(1b)

$$I_{P3} = q \int_{\Phi_{p} - \Psi_{DRIVE}}^{\Phi_{p} - E_{G}} M(E + \Psi_{DRIVE} - \Phi_{p}) T_{WKB - 3}(E) f(E) dE$$

$$(1c)$$

$$M(E) = \frac{2}{h^2} \sqrt{2m_{\rm p}E_r} f(E) = \frac{1}{1 + \exp(\frac{E}{k_{\rm B}T})}$$

(1d)

$$T_{\rm WKB-2}(E) = \exp\left(-\frac{8\pi}{3h}\sqrt{2m_{\rm p}(\Phi_{\rm p}-E)^3} \frac{\lambda}{\Psi_{\rm DRIVE}}\right)$$

(1e)

$$T_{\text{WKB}-3}(E) = \exp\left(-\frac{8\pi}{3h}\sqrt{2m_{\text{p}}E_{\text{G}}^{3}}\frac{\lambda}{\Psi_{\text{DRIVE}}}\right) \quad (1f)$$

$$\lambda = \sqrt{t_{\text{ox}}t_{\text{body}}}\frac{\varepsilon_{\text{body}}}{\varepsilon_{\text{ox}}} = \sqrt{t_{\text{ox}}t_{\text{body}}}\frac{\varepsilon_{\text{environment}}}{\varepsilon_{\text{ox}}}$$

$$\approx \sqrt{t_{\text{ox}}t_{\text{body}}} \quad (1g)$$

We have used Landauer formalism in order to calculate both the thermionic  $(I_{P1})$  and the tunneling  $(I_{P2} \text{ and } I_{P3})$ components of the source to drain current in units of A/m. In the above equations, q is the electronic charge, h is the Plank constant,  $k_{\rm B}$  is Boltzmann constant, and T is the temperature. M(E) (in units of  $(eV \cdot m \cdot s)^{-1}$ ) is the number of conducting modes (product of the density of states D(E) and the average velocity v(E) in the channel of the transistor corresponding to a 2-D parabolic band structure; f(E) is the Fermi distribution, and  $T_{WKB-2}(E)$  and  $T_{WKB-3}(E)$  are the tunneling probabilities corresponding to the two different regimes shown in Figure 2c. WKB approximation for a triangular potential barrier has been used to calculate the tunneling probabilities.  $\Psi_{\text{DRIVE}}$  is defined as the potential in the channel of the transistor corresponding to the applied gate and drain biases (see also definition in the table of Figure 2e and discussion below);  $\lambda$  is the geometric screening length;  $m_{\rm p}$ ,  $\varepsilon_{\rm body}$ , and  $t_{\rm body}$  are the effective mass, in-plane (in the direction of transport) dielectric constant, and thickness of the channel material, respectively, and  $\varepsilon_{ox}$  and  $t_{ox}$  are the dielectric constant and the thickness of the gate oxide. For an ultrathin body channel material, the field lines between the source and the drain contacts lie more in the environment rather than inside of the channel, and therefore,  $\epsilon_{\rm body}$  should be replaced by  $\epsilon_{\rm environment}$  which in backgated transistor geometry can be assumed to be the average of the dielectric constant of air,  $\varepsilon_{\rm body}$  and  $\varepsilon_{\rm ox}.$ For our calculations, we have used  $m_p = 0.57m_0$ ,  $\varepsilon_{body} =$ 7.0,  $\varepsilon_{ox} = 3.9$ ,  $E_{G} = 1.2$  eV, and  $\Phi_{p} = 0.95$  eV.<sup>25,31</sup>

Figure 2d shows the Schottky barrier tunneling current (solid curves) as a function of the geometric screening length ( $\lambda$ ) for different  $\Psi_{\text{DRIVE}}$  values. Figure 2d also shows the experimental data (semitransparent squares and triangles) corresponding to the different oxide thicknesses and flake thicknesses extracted from Figure 2a,b. Error bars capture deviceto-device variations as shown in Figure 1d. It is interesting to note that the experimental data corresponding to 100 nm back gate oxide for different flake thicknesses lie close to the contour  $\Psi_{\text{DRIVE}}$  = 5.0 V, and the experimental data corresponding to 20 nm back gate oxide for different flake thicknesses lie close to the contour  $\Psi_{\text{DRIVE}}$  =3.0 V in Figure 2d. In order to understand this finding, we calculated the magnitudes of  $\Psi_{\text{DRIVE}}$  from our experimental data using the following procedure.

1. Determination of  $V_{\rm FB}$ : The flat band voltage is defined as the gate bias at which the electron tunneling current from the source terminal is completely blocked and the device current is determined only by the thermionic emission over the top of the Schottky barrier (Figure 1f). For  $V_{GS} < V_{FB}$ , the slope of the log I<sub>DS</sub> versus V<sub>GS</sub> curve is a constant and is equal to  $60\gamma$  mV/decade (where  $\gamma$  is the band movement factor defined next).  $V_{FB}$ , therefore, can be approximately determined by finding the point on the subthreshold regime of the device characteristics where the slope changes from being constant (blue semitransparent dot in Figure 1c).

2. Determination of  $\gamma$ : In a field-effect transistor, the band movement in the channel is determined by factor  $\gamma = [1 + (C_{it} + C_{ch})/C_{ox}]$ , where  $C_{it}$ ,  $C_{ch}$ , and  $C_{ox}$  are the interface trap capacitance, channel capacitance, and oxide capacitance, respectively. In the subthreshold regime of the device operation, C<sub>ch</sub> is negligible and, therefore, the band movement factor remains constant and gets reflected in the subthreshold slope as  $60\gamma$ mV/decade. Therefore, from the constant slope of the log  $I_{\rm DS}$  versus  $V_{\rm GS}$  curve, the magnitude of  $\gamma$  can be extracted (see the semitransparent black right angled triangle in Figure 1c).

3. Determination of  $\Psi_{\text{DRIVE}}$ : Once  $V_{\text{FB}}$  and  $\gamma$  are extracted, the band position in the channel can be determined from the relation  $\Psi_{\text{DRIVE}} = qV_{\text{DS}} + q|(V_{\text{GS}} - q)|$  $V_{\rm min} - V_{\rm FB})/\gamma$  |. The reader should note that the band movement factor has been assumed to be the same for both the electron branch and the hole tunneling regime in the device characteristics. This assumption occurs justified because the amount of tunneling charges in the channel of the transistor remains small enough to ignore the contribution of the quantum capacitance ( $C_{ch}$ ) even for large negative  $V_{GS}$ . Moreover, since the Schottky barrier for hole injection is significantly larger than for electron injection, most of the drain voltage drop will occur close to the drain where the larger Schottky barrier results in a smaller transmission probability.

Table in Figure 2e shows the  $\Psi_{\text{DRIVE}}$  values obtained for the different MoS<sub>2</sub> transistors after extracting the flat band voltage  $V_{\rm FR}$  and the band movement factor  $\gamma$ from the experimental transfer characteristics shown in Figure 2a,b. Clearly, our first-order analysis agrees well with the numerical calculations. Note that large  $V_{\rm DS}$  values were used to enhance the channel potential  $\Psi_{\text{DRIVE}}$  which is not desirable for conventional transistor operation since the channel potential should be under gate control. However, this approach allows us here to demonstrate in a simple way tunneling through a large Schottky barrier as well as to study the impact of scaling on the tunneling current density.

Band-to-Band Tunneling in WSe2. WSe2 is another member of the transition metal dichalcogenides family which also is promising for certain next generation electronic applications.<sup>13,37</sup> Previously, we had demonstrated that, unlike MoS<sub>2</sub>, the Fermi level pinning at the

VOL.8 • NO.2 • 1681-1689 • 2014

JAI

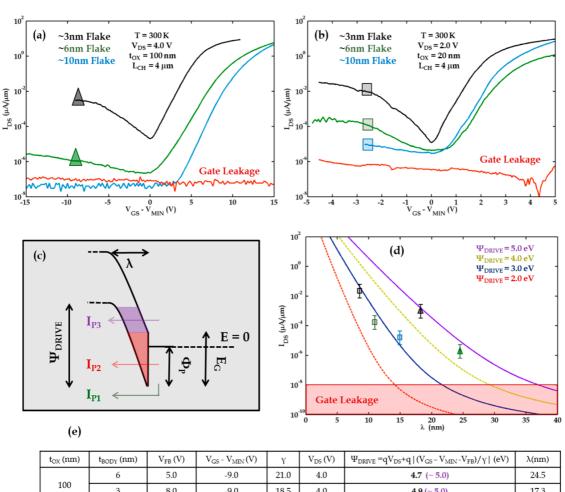

Figure 3. (a) SEM image and (b) 3-D cartoon of a 5 nm thick WSe<sub>2</sub> FET with partial top gate and full bottom gate.

metal to WSe2 interface is close to the middle of the band gap of WSe<sub>2</sub>,<sup>38</sup> which allows for both electron and hole injection into the respective energy bands.<sup>38</sup> If a p-n junction is created along a WSe<sub>2</sub> channel through electrostatic doping, the above implies that source and drain can populate the channel with both electrons and holes. Moreover, the electron and hole effective masses for the tungsten dichalcogenides are smaller compared to most of the other group VI metal chalcogenides, which is expected to result in an enhanced tunneling probability. For our first band-toband tunneling demonstration, we thus chose WSe<sub>2</sub> and adjusted the threshold voltages of the two halves of the same channel to make one region n-type and the other p-type using a partial top gate and full bottom gate geometry as shown in the SEM image and the 3D cartoon in Figure 3.

90 nm silicon dioxide (SiO<sub>2</sub>) substrate with underlying highly doped silicon was used as the back gate, and a stack of Ti/Pd was used as the source/drain metal contact. Flake of thicknesses  $\sim$ 5 nm were selected for the fabrication of the band-to-band tunneling devices. The 30 nm HfO<sub>2</sub> was deposited as the top gate dielectric using atomic layer deposition technique. The p and n regions of the device were created through electrostatic doping and could be independently controlled through the use of a partial top gate in conjunction with a full back gate as shown in Figure 3. This design allows one portion of the channel to be controlled only by the back gate, while the rest of the channel is jointly controlled by the back gate and the top gate. The entire channel of the device was 1  $\mu$ m long, while the top-gated portion was 500 nm long.

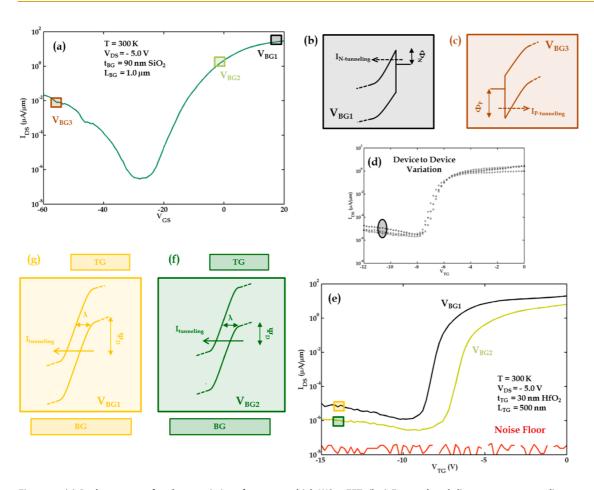

Figure 4a shows room temperature back-gated transfer characteristics of a WSe<sub>2</sub> transistor. For positive back gate voltage ( $V_{BG} > 0$ ), electrons are injected into the channel through the triangular Schottky barrier at the drain terminal (note that negative  $V_{DS}$  is applied), and for negative back gate voltage ( $V_{BG} < 0$ ), holes are injected into the channel through the triangular Schottky barrier at the source terminal.

The corresponding energy band diagrams for the electron and the hole injections are shown in Figure 4b,c. The Schottky barrier heights for the electron and the hole injection at the Ti/Pd to WSe<sub>2</sub> contacts were found to be  $\Phi_{\rm N}$  = 0.52 eV and  $\Phi_{\rm p}$  = 0.68 eV, respectively, using a similar technique as described in our earlier article.<sup>38</sup> Since the Schottky barrier height for the hole injection is higher than that for the electron injection, the hole current (at negative gate voltages) is smaller than the electron current for similar gate over drive voltages. Note that the thermionic component of the current for both the electrons and the holes are expected to be negligible compared to the corresponding thermally assisted tunneling component due to significant Schottky barriers at the source- and drain-to-channel interface.

Figure 4e shows room temperature transfer characteristics of a partially top-gated WSe<sub>2</sub> FET corresponding to two different back gate biases. Figure 4f,g shows the energy band diagrams associated with different regions of the device operation. Positive back gate biases were used to facilitate the injection of electrons into the channel. The role of the partial top gate is to control the bands in the top-gated region and thereby modulate the channel current. For positive or small negative top gate voltages,  $V_{TG}$ , the top-gated region remains n-doped (since the back gate bias is still in effect) and the device exhibits electron conduction. This is also clear from the fact that at a more positive back gate voltage ( $V_{BG1}$ ) the whole  $I_{DS} - V_{TG}$  curve (black) shifts up compared to one at lower back gate voltage ( $V_{BG2}$ ) (green curve) as well as the shift of threshold voltage. As  $V_{TG}$  is made more negative, the bands in the top-gated region move up and block the electron current injected from the drain terminal. This turns the device off. As  $V_{TG}$  becomes more negative, electrons occupying the valence band in the top-gated region start to tunnel through the band gap into the conduction band region that is controlled by the back gate. This results in an increase in the device current, as shown in Figure 3e. The reader might argue that this

VOL. 8 • NO. 2 • 1681–1689 • 2014

agnanc www.acsnano.org

Figure 4. (a) Back gate transfer characteristics of a  $\sim$ 5 nm thick WSe<sub>2</sub> FET. (b,c) Energy band diagrams corresponding to electron injection from the drain terminal and hole injection from the source terminal for the back gate biases  $V_{BG1}$  and  $V_{BG3}$ , respectively. (d) Device-to-device variations for  $\sim$ 5 nm thick WSe<sub>2</sub> top-gated FETs at  $V_{BG}$  = 20 V. (e) Top gate transfer characteristics for two different back gate biases  $V_{BG1}$  and  $V_{BG2}$ . (f,g) Energy band diagrams corresponding to band-to-band tunneling for different combinations of the top gate and the back gate biases.

current may instead be due to holes injected from the source. To eliminate this possible explanation, top gate scans were performed under different back gate biases,  $V_{BG}$ . If the current for negative top gate voltages indeed would be a result of hole injection from the source, the current value for the same top gate overdrive voltage ( $V_{TG}-V_{min}$ , where  $V_{min}$  is the point of minimum current) for  $V_{BG1} = 20$  W, which is not the case here. In fact, the observed trend is opposite. This behavior is expected for band-to-band tunneling where a larger current can flow from the valence band by tunneling into the conduction band if the potential difference in the p-n junction region is increased.

In order to further evaluate the observed band-toband tunneling current, we have used the analytical expressions shown in eq 2.

$$I_{\text{tunneling}} = q \int_0^{\Psi_{\text{D}}} M(\Psi_{\text{D}} - E) T_{\text{WKB}}(E) [f_{\text{c}}(E) - f_{\text{v}}(E)] dE \quad (2a)$$

$$f_{c}(E) = \frac{1}{1 + \exp\left(\frac{E}{k_{B}T}\right)}, \quad f_{v}(E) = \frac{1}{1 + \exp\left(\frac{E + \Psi_{D}}{k_{B}T}\right)} \quad (2b)$$

$$T_{\rm WKB}(E) = \exp\left(-\frac{8\pi}{3h}\sqrt{2m_{\rm r}E_{\rm G}^3}\frac{\lambda}{E_{\rm G}+\Psi_{\rm D}}

ight)$$

(2c)

where  $f_c$  and  $f_v$  are the occupation probabilities in the n and the p region given by the respective source and drain Fermi distributions. The interband tunneling probability is calculated using WKB approximation since it provides reasonably accurate results when compared with other detailed methods like Bardeen' transfer Hamiltonian, Landau–Zener approach etc. m<sub>r</sub> is the reduced effective mass calculated as the harmonic mean of the electron  $(m_{\rm p})$  and the hole  $(m_{\rm p})$ effective masses.<sup>39</sup> The screening length  $\lambda$  is described by a similar expression as in eq 1f but with the difference that  $\varepsilon_{environment}$  needs to be calculated as the average of the dielectric constant of the channel material, the top gate oxide, and the back gate oxide. Finally,  $\Psi_{\rm D} = q |(V_{\rm TG} - V_{\rm FB-TG})|/\gamma_{\rm TG} + q |(V_{\rm BG} - V_{\rm FB-BG})|/$  $\gamma_{BG} - E_{G}$ , where  $\gamma_{TG}$  and  $\gamma_{BG}$  are the band movement factors and  $V_{FB-TG}$  and  $V_{FB-BG}$  are the flat band voltages corresponding to the top gate and the back gate biases, respectively.

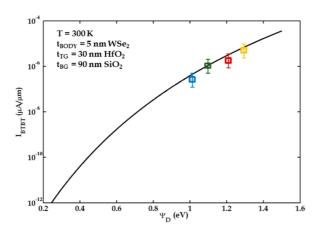

Figure 5 shows the band-to-band tunneling currents as calculated from eqs 2 as a function of  $\Psi_D$  for a

VOL. 8 • NO. 2 • 1681-1689 • 2014

IAI

www.acsnano.org

| $V_{BG}(V)$ | $V_{TG}(V)$ | $\Psi_{\rm D}~({\rm eV})$ | $I_{BTBT}$ (pA/µm) |

|-------------|-------------|---------------------------|--------------------|

| 20          | -13.8       | 1.25                      | 8.12               |

| 10          | -13.8       | 1.19                      | 3.89               |

| 0           | -13.8       | 1.09                      | 1.12               |

| -10         | -13.8       | 1.02                      | 0.32               |

Figure 5. Calculated band-to-band tunneling current levels in WSe<sub>2</sub> p-n junctions are shown as a function of the bias potential  $\Psi_{\rm D}$ . The blue, green, red, and yellow boxes are experimentally extracted data points corresponding to  $V_{\rm BG}$  = 20, 10, 0, and -10 V, respectively, as shown in the table.

5 nm thick WSe<sub>2</sub> flake with 30 nm HfO<sub>2</sub> as top gate and 90 nm SiO<sub>2</sub> as the back gate. From our experimental data, we can extract all the parameters required to calculate  $\Psi_D$  as described above. For example, we find that for  $V_{BG}$  = 20 V and  $V_{TG}$  = -13.8 V,  $\Psi_D$  = 1.3 eV, and for  $V_{BG}$  = 0 V and  $V_{TG}$  = -13.8 V,  $\Psi_D$  = 1.1 eV. The band-to-band tunneling current corresponding to these two bias points are ~8 × 10<sup>-6</sup> and ~1 × 10<sup>-6</sup>  $\mu$ A/ $\mu$ m, respectively (yellow and green semitransparent boxes in Figure 4b). The magnitude of the tunneling currents corresponding to different back gate and top gate voltages are also tabulated in Figure 5. Note that the experimental data agree well with the simulated characteristics, as shown in Figure 5.

The reader should note that with large back gate voltages it is possible to create an n-type contact underneath the metallic drain electrode at the SiO<sub>2</sub>-TMD interface. It has been widely observed in the case of graphene, which has a low density of states. There is no evidence of such gated contact area for the TMDs. In case such scenario does exist, the tunneling current extracted in this article would be a product of two tunneling probabilities, one at the channel p-n iunction and the other at the contact p-n iunction. The reader should also note that both the back gate and the top gate, in our partially gated WSe<sub>2</sub> FET, have complete control of the WSe<sub>2</sub> stack. This is evident from the transfer characteristics (Figure 4a,e) that clearly show that both the back and the top gate can individually turn the device off. Therefore, all the layers in our multilayer WSe<sub>2</sub> stack are under tight gate control (both top and back). Under different combinations of the top and the back gate bias, the entire stack is either n- or p-type-doped. A variable doping profile among the layers cannot exist which eliminates the possibility of interlayer tunneling transverse to the channel direction.

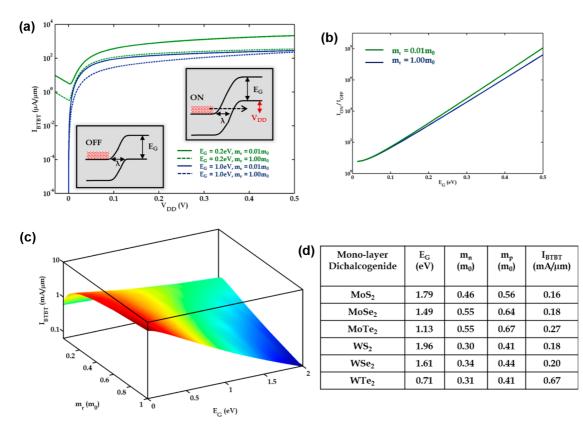

**Projections for Band-to-Band Tunneling Currents in TMDs.** Since our experimental data can be explained within reasonable degree of accuracy by our simple analytical models, we use the same to make projections for bandto-band tunneling (BTBT) currents in transition metal dichalcogenide p-n homojunctions (see inset of Figure 6a) which are the basic building blocks for TFETs. One of the major obstacles in the implementation of TFET is its poor drive current capability limited by the transmission through large tunneling barriers that exist in these p-n junctions. The tunneling current in such p-n junction is given by the set of eqs 2 with  $\Psi_{\mathsf{D}}$  being replaced by the applied bias  $qV_{DD}$  if we assume that scattering inside the p or n channel does not impact the current. As evident from the equations, thinner gate oxides and thinner channels are desired to reduce the magnitude of  $\lambda$  and hence increase the tunneling probability. Layered two-dimensional dichalcogenides with ultrathin body thicknesses are, therefore, desirable in the context of TFETs as significantly higher tunneling current densities could be achieved. Material parameters like the band gap  $(E_G)$  and the effective mass  $(m_r)$  also play an equally important role in determining the tunneling probability. Figure 6a shows the band-to-band tunneling currents (I<sub>BTBT</sub>) as a function of the bias voltage  $V_{DD}$  in logarithmic scale based on hypothetical 2-D materials ( $d_{body} = 1 \text{ nm}$ ) with different combinations of band gap ( $E_G$ ) and reduced effective mass  $(m_r)$ . The effective oxide thickness (EOT) was assumed to be 1 nm. As seen in Figure 6a, smaller band gaps improve the on-state drive current density but at the expense of a degraded off-state performance. This is because in this case a substantial thermionic emission current can flow from the n region to the p region. Figure 6b shows that the ratio of the on-state band-to-band tunneling current to the offstate thermionic emission current changes exponentially as a function of  $E_{\rm G}$  for any given  $m_{\rm r}$ . Figure 6b also suggests that the on-off ratio is not impacted significantly by the effective mass. Figure 6c shows the onstate drive current density as a function of both  $m_{\rm r}$ and  $E_{G}$ . It is interesting to note that there exists a local maximum for the drive current density as a function of the effective mass corresponding to each different band gap. This local maximum is an outcome of two

VOL.8 • NO.2 • 1681-1689 • 2014

agnanc www.acsnano.org

Figure 6. (a) Band-to-band tunneling current ( $I_{BTBT}$ ) in logarithmic scale as a function of the bias  $V_{DD}$  for different combinations of band gaps and effective masses. The cartoons in the inset show the basic operation principal. (b) Ratio of on-state tunneling current to the off-state thermionic current as a function of the band gap for different effective masses. (c) Band-to-band tunneling current for a given bias  $V_{DD} = 0.5$  V as a function of both the effective mass and the band gap. (d) Table shows the band gap, electron, and hole effective masses and  $I_{BTBT}$  for 0.5 V supply voltage for various monolayer TMDs calculated using the model described in the text.

counteracting effects—smaller values for  $m_r$  improve the tunneling probability but at the same time reduce the number of conducting modes. Since the tunneling current is a product of the number of conducting modes and the tunneling probability, a local maximum exists for each  $E_G$ . Given the requirement for CMOS logic circuit design which demands a minimum on—off ratio of 10<sup>4</sup>, the band gap  $E_G$  should be chosen to be larger than 0.3 eV.

The above-described situation is, however, far from reality where  $E_{\rm G}$  and  $m_{\rm r}$  are coupled through the energy dispersion relationship and, therefore, cannot be tuned independently for any material. Also for the same material, these parameters depend strongly on the body thickness. The table in Figure 6d shows the magnitude of the band gap ( $E_{\rm G}$ ), electron effective mass ( $m_{\rm n}$ ), and hole effective mass ( $m_{\rm p}$ )<sup>40,41</sup> and the corresponding band-to-band tunneling currents for  $V_{\rm DD} = 0.5$  V in a p-n homojunction made from various monolayer transition metal dichalcogenides. Note that the effective mass  $m_{\rm r}$  has been calculated as the harmonic mean of  $m_{\rm n}$  and  $m_{\rm p}$ . Monolayer WTe<sub>2</sub>, by the

virtue of its smaller band gap, outperforms all other dichalcogenides with  $I_{BTBT}$  of ~0.67 mA/ $\mu$ m. Among the dichalcogenides which have been widely studied as the channel material for field-effect transistors, WSe<sub>2</sub> and MoTe<sub>2</sub> appear to be better choices for tunneling applications. Our analysis provides initial basic insights into the material parameters that are important in the context of tunneling and thereby helps in identifying the ideal 2-D material for TFET applications.

### CONCLUSION

In conclusion, we experimentally demonstrated for the first time hole tunneling currents through triangular Schottky barriers in MoS<sub>2</sub> back-gated FETs and band-to-band tunneling currents in double-gated WSe<sub>2</sub> FETs. We found that by scaling the geometric screening length  $\lambda$ , the tunneling current can be increased by orders of magnitude. Finally, we also used our experimental data and analytical calculations to provide projections for band-to-band tunneling currents for monolayer dichalcogenides.

#### **METHODS**

$MoS_2$  flakes were mechanically exfoliated onto 20 and 100 nm silicon dioxide substrates with underlying highly doped

silicon. Flake thicknesses were first identified approximately through optical contrast and then accurately determined by atomic force microscopy. Electron beam lithography followed

VOL. 8 • NO. 2 • 1681-1689 • 2014 A

A fabrication process similar to the one described above for  $MoS_2$  FETs was used to create back-gated  $WSe_2$  FETs with Ti/Pd contacts on a 90 nm SiO<sub>2</sub> substrate with underlying highly doped silicon. Flakes thicknesses ~5 nm thick were selected for the fabrication of the band-to-band tunneling devices. The 30 nm HfO<sub>2</sub> was deposited as the top gate dielectric using atomic layer deposition techniques.

Conflict of Interest: The authors declare no competing financial interest.

Acknowledgment. We would like to thank Professor Di Xiao for providing data on the effective masses for the transition metal dichalcogenides based on their DFT calculations (GGA method without spin orbit coupling). This work was in part supported by the STARnet center LEAST, a Semiconductor Research Corporation program sponsored by MARCO and DARPA.

### **REFERENCES AND NOTES**

- Kuhn, K. J. Considerations for Ultimate CMOS Scaling. IEEE Trans. Electron Devices 2012, 59, 1813–1828.

- Nowak, E. J. Advanced CMOS Scaling and FinFET Technology. ECS Trans. 2012, 50, 3–16.

- Skotnicki, T.; Hutchby, J. A.; King, T. Toward the Introduction of New Materials and Structural Changes To Improve MOSFET Performance. *IEEE Circuit Device Mag.* 2005, 21, 16–26.

- Lu, W.; Xie, P.; Lieber, C. M. Nanowire Transistor Performance Limits and Applications. *IEEE Trans. Electron Devices* 2008, 55, 2859–2876.

- Appenzeller, J.; Knoch, J.; Björk, M. T. Toward Nanowire Electronics. *IEEE Trans. Nanotechnol.* 2008, 55, 2827–2845.

- McEuen, P. L.; Fuhrer, M. S. Single-Walled Carbon Nanotube Electronics. *IEEE Trans. Nanotechnol.* 2002, 1, 78–85.

- Appenzeller, J.; Knoch, J.; Martel, R.; Derycke, V.; Wind, S. J.; Member, S.; Avouris, P. Carbon Nanotube Electronics. *IEEE Trans. Nanotechnol.* 2002, 1, 184–189.

- del Alamo, J. A. Nanometre-Scale Electronics with III-V Compound Semiconductors. *Nature* 2011, 479, 317–323.

- 9. Palacios, T. Graphene Electronics: Thinking Outside the Silicon Box. *Nat. Nanotechnol.* **2011**, *6*, 464–465.

- 10. Geim, A. K.; Novoselov, K. S. The Rise of Graphene. *Nat. Mater.* **2007**, *6*, 183–191.

- Radisavljevic, B.; Radenovic, A.; Brivio, J.; Giacometti, V.; Kis, A. Single-Layer MoS<sub>2</sub> Transistors. *Nat. Nanotechnol.* 2011, 6, 147–150.

- Kim, S.; Konar, A.; Hwang, W.-S.; Lee, J. H.; Lee, J.; Yang, J.; Jung, C.; Kim, H.; Yoo, J.-B.; Choi, J.-Y.; *et al.* High-Mobility and Low-Power Thin-Film Transistors Based on Multilayer MoS<sub>2</sub> Crystals. *Nat. Commun.* **2012**, *3*, 1011.

- Liu, W.; Kang, J.; Sarkar, D.; Khatami, Y.; Jena, D.; Banerjee, K. Role of Metal Contacts in Designing High-Performance Monolayer n-Type WSe<sub>2</sub> Field Effect Transistors. *Nano Lett.* **2013**, *13*, 1983–1990.

- Wang, Q. H.; Kalantar-Zadeh, K.; Kis, A.; Coleman, J. N.; Strano, M. S. Electronics and Optoelectronics of Two-Dimensional Transition Metal Dichalcogenides. *Nat. Nanotechnol.* **2012**, *7*, 699–712.

- Appenzeller, J.; Lin, Y.-M.; Knoch, J.; Avouris, P. Band-to-Band Tunneling in Carbon Nanotube Field-Effect Transistors. *Phys. Rev. Lett.* **2004**, *93*, 196805.

- Ionescu, A. M.; Riel, H. Tunnel Field Effect Transistors as Energy Efficient Electronic Switches. *Nature* 2011, 479, 329–337.

- Choi, W. Y.; Park, B.; Lee, J. D.; Liu, T. K. Tunneling Field-Effect Transistors (TFETs) with Subthreshold Swing (SS) Less Than 60 mV/dec. *IEEE Electron Device Lett.* **2007**, *28*, 743–745.

- Smith, J. T.; Das, S.; Appenzeller, J. Broken-Gap Tunnel MOSFET: A Constant-Slope Sub-60-mV/decade Transistor. *IEEE Electron Device Lett.* 2011, 32, 1367–1369.

- Gopalakrishnan, K.; Griffin, P. B.; Plummer, J. D. Impact Ionization MOS (I-MOS)—Part I: Device and Circuit Simulations. *IEEE Trans. Electron Devices* 2005, *52*, 69–76.

- Gopalakrishnan, K.; Woo, R.; Jungemann, C.; Griffin, P. B.; Plummer, J. D. Impact Ionization MOS (I-MOS)—Part II: Experimental Results. *IEEE Trans. Electron Devices* 2005, *52*, 77–84.

- Akarvardar, K.; Eggimann, C.; Tsamados, D.; Chauhan, Y. S.; Wan, G. C.; Ionescu, A. M.; Member, S.; Howe, R. T.; Wong, H. P. Analytical Modeling of the Suspended-Gate FET and Design Insights for Low-Power Logic. *IEEE Trans. Electron Devices* 2008, *55*, 48–59.

- Salahuddin, S.; Datta, S. Use of Negative Capacitance To Provide Voltage Amplification for Low Power Nanoscale Devices. *Nano Lett.* 2008, *8*, 405–410.

- 23. Das, S.; Appenzeller, J. On the Importance of Bandgap Formation in Graphene for Analog Device Applications. *IEEE Trans. Nanotechnol.* **2011**, *10*, 1093–1098.

- He, K.; Poole, C.; Mak, K. F.; Shan, J. Experimental Demonstration of Continuous Electronic Structure Tuning via Strain in Atomically Thin MoS<sub>2</sub>. Nano Lett. **2013**, *13*, 2931–2936.

- Kumar, A.; Ahluwalia, P. K. Electronic Structure of Transition Metal Dichalcogenides Monolayers 1H-MX2 (M = Mo, W; X = S, Se, Te) from *Ab-Initio* Theory: New Direct Band Gap Semiconductors. *Eur. Phys. J. B* **2012**, *85*, 186.

- Johari, P.; Shenoy, V. B. Tuning the Electronic Properties of Semi- conducting Transition Metal Dichalcogenides by Applying Mechanical Strains. ACS Nano 2012, 6, 5449– 5456.

- Splendiani, A.; Sun, L.; Zhang, Y.; Li, T.; Kim, J.; Chim, C.-Y.; Galli, G.; Wang, F. Emerging Photoluminescence in Monolayer MoS<sub>2</sub>. *Nano Lett.* **2010**, *10*, 1271–1275.

- Baugher, B. W. H.; Churchill, H. O. H.; Yang, Y.; Jarillo-Herrero, P. Intrinsic Electronic Transport Properties of High-Quality Monolayer and Bilayer MoS<sub>2</sub>. *Nano Lett.* **2013**, *13*, 4212–4216.

- Liu, K.-K.; Zhang, W.; Lee, Y.-H.; Lin, Y.-C.; Chang, M.-T.; Su, C.-Y.; Chang, C.-S.; Li, H.; Shi, Y.; Zhang, H.; *et al.* Growth of Large-Area and Highly Crystalline MoS<sub>2</sub> Thin Layers on Insulating Substrates. *Nano Lett.* **2012**, *12*, 1538–1544.

- Wang, H.; Yu, L.; Lee, Y.-H.; Shi, Y.; Hsu, A.; Chin, M. L.; Li, L.-J.; Dubey, M.; Kong, J.; Palacios, T. Integrated Circuits Based on Bilayer MoS<sub>2</sub> Transistors. *Nano Lett.* **2012**, *12*, 4674– 4680.

- Das, S.; Chen, H.-Y.; Penumatcha, A. V.; Appenzeller, J. High Performance Multilayer MoS<sub>2</sub> Transistors with Scandium Contacts. *Nano Lett.* **2013**, *13*, 100–105.

- 32. Das, S.; Appenzeller, J. Where Does the Current Flow in Two-Dimensional Layered Systems? *Nano Lett.* **2013**, *13*, 3396–3402.

- Das, S.; Appenzeller, J. Screening and Interlayer Coupling in Multilayer MoS<sub>2</sub>. *Phys. Status Solidi RRL* 2013, *4*, 268– 273.

- Das, S.; Appenzeller, J. Evaluating the Scalability of Multilayer MoS<sub>2</sub> Field Effect Transistor. *Device Res. Conf.* 2013.

Lundstrom, M.; Guo, J. *Nanoscale Transistors: Device Physics*,

- Modeling and Simulation; Springer: Berlin, 2006.

- Datta, S. Quantum Transport: Atom to Transistor; Cambridge University Press: Cambridge, 2005.

- Liu, L.; Kumar, S. B.; Ouyang, Y.; Guo, J. Performance Limits of Monolayer Transition Metal Dichalcogenide Transistors. *IEEE Trans. Electron Devices* 2011, 58, 3042–3047.

- Das, S.; Appenzeller, J. WSe<sub>2</sub> Field Effect Transistors with Enhanced Ambipolar Characteristics. *Appl. Phys. Lett.* 2013, 103, 103501.

- Ma, N.; Jena, D. Interband Tunneling in Two-Dimensional Crystal Semiconductors. Appl. Phys. Lett. 2013, 102, 132102.

- Liu, G.-B.; Shan, W.-Y.; Yao, Y.; Yao, W.; Xiao, D. Three-Band Tight-Binding Model for Monolayers of Group-VIB Transition Metal Dichalcogenides. *Phys. Rev. B.* 2013, *88*, 085433.

- Liu, L.; Kumar, S. B.; Ouyang, Y.; Guo, J. Performance Limits of Monolayer Transition Metal Dichalcogenide Transistors. *IEEE Trans. Electron Devices* 2011, 58, 3042–3047.